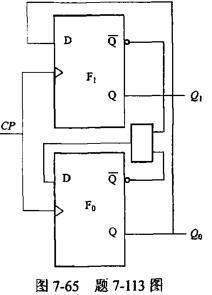

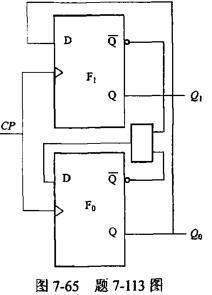

如图7-65所示电路中,两个D触发器在接受触发脉冲前为均为0,分析电路,该电路是()。A.异步二进制计数器B.左移计数器C.右移计数器D.同步三进制计数器

如图7-65所示电路中,两个D触发器在接受触发脉冲前为均为0,分析电路,该电路是()。

A.异步二进制计数器

B.左移计数器

C.右移计数器

D.同步三进制计数器

A.异步二进制计数器

B.左移计数器

C.右移计数器

D.同步三进制计数器

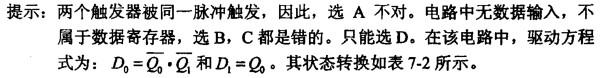

参考解析

解析:正确答案是D。

相关考题:

在异步时序电路的分析和设计中,采取了下列修改和补充考虑()。 A、输入信号及触发器的时钟信号有脉冲用1表示,无脉冲用0表示B、次态逻辑的输出包括触发器的控制输出和时钟输入C、两个或两个以上的输入变量不能同时为一;输入全为零时,电路状态不变D、在设计时,状态变化(即状态由0到1,1到0),令CLK=1

由两个主从型JK触发器组成的逻辑电路如图a)所示,设Q1、Q2的初始态是0、0, 已知输入信号A和脉冲信号CP的波形,如图b)所示,当第二个CP脉冲作用后,Q1、Q2将变为:A. 1、1B. 1、0C. 0、1D.保持0、0不变

图(a)所示电路中,时钟脉冲、复位信号及数模信号如图(b)所示,经分析可知,在第一个和第二个时钟脉冲的下降沿过后,输出Q先后等于( )。附:触发器的逻辑状态表为:A、 00B、 01C、 10D、 11

图(a)所示电路中,复位信号及时钟脉冲信号如图(b)所示,经分析可知,在t1时刻,输出QJK和QD分别等于( )。附:D触发器的逻辑状态表为:JK触发器的逻辑状态表为:A.00B.01C.10D.11

由两个主从型JK触发器组成的电路如图(a)所示,设Q1、Q2的初始态是00,已知输入信号A和脉冲信号CP的波形,如图(b)所示,当第一个CP脉冲作用后,输出将为( )。A.00B.01C.10D.11

CMOS集成施密特触发器组成的电路如图(a)所示,该施密特触发器的电压传输特性曲线如图(b)所示,该电路的功能为( )。 A. 双稳态触发器 B. 单稳态触发器 C. 多谐振荡器 D. 三角波发生器

用3个D触发器组成的电路如图7-67所示,触发器F0的输入端接+5V表明D0=1,那么,在第1个CP脉冲和第2个脉冲的上升沿过后分别是()。A.101和011 B.011和111 C.001和011 D.000和111

用3个D触发器组成的电路如图7-69所示,触发器F0的输入端接+5V表明D0=1,那么,在第1个CP脉冲和第2个脉冲的上升沿过后Q2Q1Q0分别是()。A、101和011B、011和111C、001和011D、000和111

在大功率晶闸管触发电路中,常采用脉冲列式触发器,其目的是减小触发电源功率、减小脉冲变压器的体积,还能()。A、减小触发电路元器件数量B、省去脉冲形成电路C、提高脉冲前沿陡度D、扩展移相范围