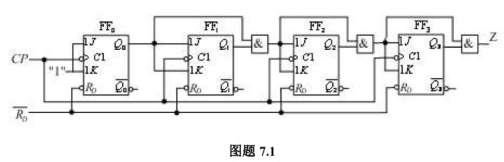

计数器电路如图题7.1所示。设各触发器的初始状态均为“0”,分析该电路的逻辑功能。

计数器电路如图题7.1所示。设各触发器的初始状态均为“0”,分析该电路的逻辑功能。

相关考题:

如图7-65所示电路中,两个D触发器在接受触发脉冲前为均为0,分析电路,该电路是()。A.异步二进制计数器B.左移计数器C.右移计数器D.同步三进制计数器

计数器电路如图题7.1所示。设各触发器的初始状态均为“0”,分析该电路的逻辑功能。