计数器电路如图题7.3所示。设各触发器的初始状态均为“0”,要求:(1) 写出各触发器的驱动方程和次态方程;(2)画出次态卡诺图;画出状态转换图并说明该计数器电路的逻辑功能;

试分析图题7.8的计数器电路,说明这是多少进制的计数器。

试用上升沿D触发器构成异步3位二进制加法计数器,要求画出逻辑电路图,以及计数器输入时钟CLK与D触发器输出端Q2~Q0的波形图。

试用上升沿JK触发器构成同步3位二进制加法计数器,要求画出逻辑电路图。

图题6-25所示为具有同步清除功能的同步四位二进制加法计数器74LS163组成的计数器电路,试说明该计数电路是多少进制。

图题6-26所示为具有异步清除功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该计数电路是多少进制。

图题6-27所示为具有同步预置功能的同步四位二进制加法计数器74LS161组成的计数电路,试说明该计数电路是多少进制。

试判断图题6-29所示为电路为多少进制计数器,是同步电路还是异步电路。

图(a)所示时序逻辑电路的工作波形如图(b)所示,由此可知,图(a)电路是一个( )。A.右移寄存器B.三进制计数器C.四进制计数器D.五进制计数器

图示时序逻辑电路是一个( )。附:触发器的逻辑状态表为:A、左移寄存器B、右移寄存器C、异步三位二进制加法计数器D、同步六进制计数器

采用中规模加法计数器74LS161构成的电路如图所示,该电路构成几进制加法计数器( )。 A. 九进制 B. 十进制 C. 十二进制 D. 十三进制

由四位二进制同步计算器74161构成的逻辑电路如图所示,该电路的逻辑功能为( )。A.同步256进制计数器C.同步217进制计数器B.同步243进制计数器D.同步196进制计数器

A.同步二进制加法计数器B.同步二进制减法计数器C.异步二进制减法计数器D.异步二进制加法计数器

图所示逻辑电路,设触发器的初始状态均为0,当时,该电路实现的逻辑功能是( )。A.同步十进制加法计数器B.同步八进制加法计数器C.同步六进制加法计数器D.同步三进制加法计数器

图所示逻辑电路,设触发器的初始状态均为“0”。当RD=1时,该电路的逻辑功能为( )。A.同步八进制加法计数器B.同步八进制减法计数器C.同步六进制加法计数器D.同步六进制减法计数器

采用中规模加法计数器74LS161构成的计数器电路如图所示,该电路的进制为( )。 A. 十一进制 B. 十二进制 C. 八进制 D. 七进制

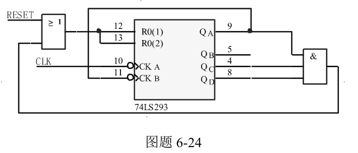

图示电路的逻辑功能为( )。 A. 异步8进制计数器 B. 异步7进制计数器 C. 异步6进制计数器 D. 异步5进制计数器

图示的74LS161集成计数器构成的计数器电路和74LS290集成计数器构成的计数器电路是实现的逻辑功能依次是( )。 A. 九进制加法计数器,七进制加法计数器 B. 六进制加法计数器,十进制加法计数器 C. 九进制加法计数器,六进制加法计数器 D. 八进制加法计数器,七进制加法计数器

在图示电路中,当开关A、B、C分别闭合时,电路所实现的功能分别为( )。 A. 8、4、2进制加法计数器 B. 16、8、4进制加法计数器 C. 4、2进制加法计数器 D. 16、8、2进制加法计数器

如图所示异步时序电路,该电路的逻辑功能为( )。 A. 八进制加法计数器 B. 八进制减法计数器 C. 五进制加法计数器 D. 五进制减法计数器

如图7-65所示电路中,两个D触发器在接受触发脉冲前为均为0,分析电路,该电路是()。A.异步二进制计数器B.左移计数器C.右移计数器D.同步三进制计数器

下列电路中,不属于时序逻辑电路的是()A、同步加法计数器B、全加器C、寄存器D、异步减法计数器

计数器按计数工作方式分为()。A、同步计数器和异步计数器B、二进制计数器和非二进制计数器C、加法计数器和减法计数器D、扭环形计数器和环形计数器

电路中各触发器状态改变有先有后是异步的,用它作成的计数器是()。A、同步计数器B、异步计数器C、二进制计数器D、四进制计数器

同步二进制计数器的电路比异步二进制计数器复杂,所以实际应用中较少使用同步二进制计数器。

单选题下列电路中,不属于时序逻辑电路的是()A同步加法计数器B全加器C寄存器D异步减法计数器

单选题电路中各触发器状态改变有先有后是异步的,用它作成的计数器是()。A同步计数器B异步计数器C二进制计数器D四进制计数器