触发器按其工作状态是否稳定可分为() A、RS触发器,JK触发器,D触发器,T触发器B、双稳态触发器,单稳态触发器,无稳态触发器C、主从型触发器,维持阻塞型触发器。

已知电路及输入信号波形如图4-13所示.试画出主从JK触发器的Q'.Q端的波形,触发器初始状态为0.

在图4-33(a)所示各电路图中,CP.A.B的波形如图4-33(b)所示.(1)写出触发器次态Qn+1的函数表达式.(2)画出Q1、Q2.Q3、Q4的波形图.假设各触发器初始状态均为0.

计数器电路如图题7.1所示。设各触发器的初始状态均为“0”,分析该电路的逻辑功能。

计数器电路如图题7.3所示。设各触发器的初始状态均为“0”,要求:(1) 写出各触发器的驱动方程和次态方程;(2)画出次态卡诺图;画出状态转换图并说明该计数器电路的逻辑功能;

画出图题5-9所示的正边沿触发JK触发器输出Q端的波形,输入端J、K与CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-14所示各触发器输出Q端的波形,CLK、 A和B的波形如图所示。(设Q初始状态为0)

试画出图题5-15所示各触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-18所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0)

画出图题5-10所示的JK触发器输出端Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

画出图题5-6所示的边沿D触发器输出Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

画出图题5-8所示的JK触发器输出Q端的波形,输入端JK与CLK的波形如图示。(设Q初始状态为0)

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

JK触发器及其输入信号波形如图所示,该触发器的初值为0,则它的输出Q为:

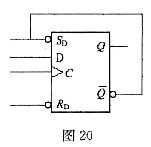

逻辑电路如图所示,当A=“0”,B=“1”时,C脉冲来到后,D触发器应( )。 A.具有计数功能B.保持原状态C.置“0”D.置“1”

图(a)所示电路中,复位信号及时钟脉冲信号如图(b)所示,经分析可知,在t1时刻,输出QJK和QD分别等于( )。附:D触发器的逻辑状态表为:JK触发器的逻辑状态表为:A.00B.01C.10D.11

JK触发器及其输入信号波形图如图所示,该触发器的初值为0,则它的输出Q为:

JK触发器外部连接如图所示,则其输出可表达为( )。

CMOS集成施密特触发器组成的电路如图(a)所示,该施密特触发器的电压传输特性曲线如图(b)所示,该电路的功能为( )。 A. 双稳态触发器 B. 单稳态触发器 C. 多谐振荡器 D. 三角波发生器

JK触发器构成的电路如图所示,该电路能实现的功能是( )。A.RS触发器B.D触发器C.T触发器D.T′触发器

由CMOS集成施密特触发器组成的电路及该施密特触发器的电压传输特性曲线如图所示,该电路组成了一个()。A.存储器 B.单稳态触发器 C.反相器 D.多谐振荡器

在如图7-72所示的RS触发器,设Q的初始状态为1,当输入X信号后,输出Q为()。A.X B.X C.1 D.0

一个只有单端输入的边沿触发器,输入信号为0,原来所处状态Q=1,在时钟信号改变时,触发器状态Q变为0,则该触发器为()。A、RS触发器B、JK触发器C、D触发器D、T触发器