已知电路及输入信号波形如图4-13所示.试画出主从JK触发器的Q'.Q端的波形,触发器初始状态为0.

试分别画出图4-30(a)电路输出端Y、Z和图4-30(b)电路输出端Q2的波形.输入信号A和CP的电压波形如图4-30(c)所示,各触发器的初始状态为0.

试画出图4-15中各触发器Q端波形.设初始状态均为0.

试画出图题5-14所示各触发器输出Q端的波形,CLK、 A和B的波形如图所示。(设Q初始状态为0)

试画出图题5-15所示各触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

画出图题5-4所示的电平触发D触发器输出Q端的波形,输入端D与CLK的波形如图所示。(设0初始状太为0)

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0)

画出图题5-2所示的SR锁存器输出端Q、Q—端的波形,输入端S与R的波形如图所示。(设Q初始状态为0)

画出图题5-10所示的JK触发器输出端Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

画出图题5-1所示的SR锁存器输出端Q、端的波形,输入端与的波形如图所示。(设Q初始状态为0)

画出图题5-6所示的边沿D触发器输出Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

试画出图题5-12所示电路输出端Q1、Qo端的波形,CLK 的波形如图所示。(设Q初始状态为0)

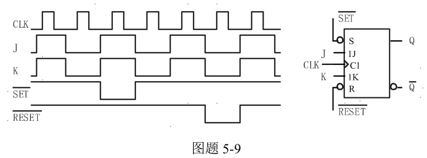

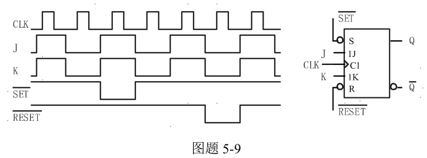

画出图题5-8所示的JK触发器输出Q端的波形,输入端JK与CLK的波形如图示。(设Q初始状态为0)

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

图题6-15所示的是5位右移寄存器与输入信号DATA、时钟CLK的波形图,若寄存器初始状态为00000,试画出寄存器输出Q4~Q0的波形图。

试用上升沿D触发器构成异步3位二进制加法计数器,要求画出逻辑电路图,以及计数器输入时钟CLK与D触发器输出端Q2~Q0的波形图。

JK触发器及其输入信号波形如图所示,该触发器的初值为0,则它的输出Q为:

JK触发器及其输入信号波形图如图所示,该触发器的初值为0,则它的输出Q为:

逻辑电路图及相应的输入CP、A、B的波形分别如图所示,初始状态Q1=Q2=0,当RD=1时,D、Q1、Q2端输出的波形分别是( )。

欲使JK触发器按Qn+1=1工作,可使JK触发器的输入端()。A、J=K=1B、J=1,K=0C、J=K=Q’D、J=K=0E、J=Q’,K=0

欲使JK触发器按Qn+1=Q’n工作,可使JK触发器的输入端()。A、J=K=1B、J=Q,K=Q’C、J=Q’,K=QD、J=Q,K=1E、J=1,K=Q

欲使JK触发器按Qn+1=Qn工作,可使JK触发器的输入端()。A、J=K=0B、J=Q,K=Q’C、J=Q’,K=QD、J=Q,K=0E、J=0,K=Q’

欲使JK触发器按Qn+1=0工作,可使JK触发器的输入端()A、J=K=1B、J=Q,K=QC、J=Q,K=1D、J=0,K=1

欲使JK触发器按工作,可使JK触发器的输入端()。A、J=K=1B、J=Q,K=QC、J=K=0D、J=1,K=0