要使JK触发器的输出Q从1变成0,它的输入信号JK应为( ) A.00B.01C.10D.都不行

要使JK触发器的输出Q从1变成0,它的输入信号J、K应为()。 A、00B、01C、10

已知电路及输入信号波形如图4-13所示.试画出主从JK触发器的Q'.Q端的波形,触发器初始状态为0.

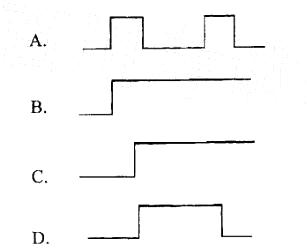

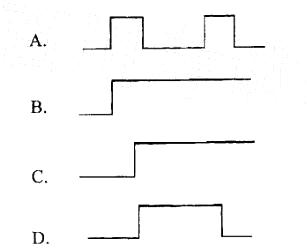

画出图题5-9所示的正边沿触发JK触发器输出Q端的波形,输入端J、K与CLK的波形如图所示。(设Q初始状态为0)

画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0)

画出图题5-10所示的JK触发器输出端Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

画出图题5-8所示的JK触发器输出Q端的波形,输入端JK与CLK的波形如图示。(设Q初始状态为0)

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

试用上升沿D触发器构成异步3位二进制加法计数器,要求画出逻辑电路图,以及计数器输入时钟CLK与D触发器输出端Q2~Q0的波形图。

JK触发器及其输入信号波形如图所示,那么,在t=t0和t=t1时刻,输出Q分别为:

JK触发器及其输入信号波形如图所示,该触发器的初值为0,则它的输出Q为:

JK触发器,当J=1,K=0,该触发器的状态为( )。A 置“0”B 置“1”C 不变D 计数

D触发器的应用电路如图所示,设输出Q的初值为0,那么,在时钟脉冲cp的作用下,输出Q为:A.1B.cpC.脉冲信号,频率为时钟脉冲频率的1/2D.0

JK触发器及其输入信号波形图如图所示,该触发器的初值为0,则它的输出Q为:

JK触发器及其输入信号波形如图所示,那么,在t=t0和t = t1时刻,输出Q分别为:A. Q(t0)= 1,Q(t1)=0 B. Q(t0)= 0,Q(t1)=1 C. Q(t0)= 0,Q(t1)=0 D.Q(t0)= 1,Q(t1)=1

JK触发器外部连接如图所示,则其输出可表达为( )。

D触发器的应用电路如图所示,设输出Q的初值为0,那么,在时钟脉冲CP的作用下,输出Q为:A. 1B. CPC.脉冲信号,频率为时钟脉冲频率的1/2D.0

若JK触发器Q*=Q’,则输入(J,K)=()。如果用D触发器完成相同功能,则D=()

欲使JK触发器按Qn+1=1工作,可使JK触发器的输入端()。A、J=K=1B、J=1,K=0C、J=K=Q’D、J=K=0E、J=Q’,K=0

欲使JK触发器按Qn+1=Qn工作,可使JK触发器的输入端()。A、J=K=0B、J=Q,K=Q’C、J=Q’,K=QD、J=Q,K=0E、J=0,K=Q’

欲使JK触发器按Qn+1=0工作,可使JK触发器的输入端()A、J=K=1B、J=Q,K=QC、J=Q,K=1D、J=0,K=1

要使JK触发器的输出Q从1就成0,它的输入信号JK就为()。A、00B、01C、10D、无法确定

欲使JK触发器按工作,可使JK触发器的输入端()。A、J=K=1B、J=Q,K=QC、J=K=0D、J=1,K=0

两个与非门构成的基本RS触发器,当Q=1、Q=0时,两个输入信号R=1和S=1。触发器的输出Q会()。A、变为0B、保持1不变C、保持0不变D、无法确定

要使JK触发器的输出Q从1变成0,它的输入信号JK应为();A、00B、01C、10D、无法确定

一个只有单端输入的边沿触发器,输入信号为0,原来所处状态Q=1,在时钟信号改变时,触发器状态Q变为0,则该触发器为()。A、RS触发器B、JK触发器C、D触发器D、T触发器

对于下降沿触发的D触发器,当时钟CP由1变为0时,触发器的状态Q由0变为1,则该触发器的输入端D为()。A、无法判断B、任意值C、0D、1