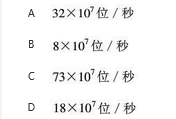

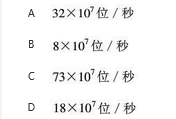

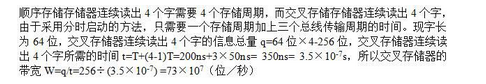

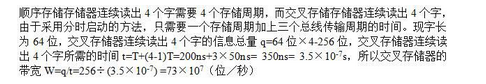

设存储器容量为32字,字长64位,模块数m=4,存储周期T=200ns,数据总线宽度为64位,总线传送周期τ=50ns。用交叉方式进行组织,交叉存储器的带宽是()。

设存储器容量为32字,字长64位,模块数m=4,存储周期T=200ns,数据总线宽度为64位,总线传送周期τ=50ns。用交叉方式进行组织,交叉存储器的带宽是()。

参考解析

解析:

相关考题:

请教:2010年下半年软考软件设计师-上午试题(标准参考答案版)第1大题第3小题如何解答?【题目描述】● 若内存容量为4GB,字长为32,则(3) 。(3)A.地址总线和数据总线的宽度都为 32B.地址总线的宽度为30,数据总线的宽度为 32C.地址总线的宽度为30,数据总线的宽度为 8D.地址总线的宽度为32,数据总线的宽度为 8

若内存容量为4GB,字长为32,则(3)。A.地址总线和数据总线的宽度都为32B.地址总线的宽度为30,数据总线的宽度为32C.地址总线的宽度为30,数据总线的宽度为8D.地址总线的宽度为32,数据总线的宽度为8

主存DRAM芯片保持所存数据不丢失的方法是(176)。当需要扩大空量时,可采用字扩展法,它是(177)。为提高内存数据读取速度采用了不少方法,但(178)不属于这个目的。假设内存存取周期T=200ns,字长64位,数据总线宽度64位,总线传周期为50ns。现用4个模块组成内存,并在连续4个地址中读出数据。如用顺序方式组织模块,则数据带宽为(179)。如用交叉存储方式组织内存,则数据带宽可达约(180)。A.定时逐个地址刷新B.对读出数据单元的立即刷新C.定时成组刷新D.确保内存电源稳定供电

若内存容量为4GB,字长为32,则______。A.地址总线和数据总线的宽度都为32B.地址总线的宽度为30,数据总线的宽度为32C.地址总线的宽度为30,数据总线的宽度为8D.地址总线的宽度为32,数据总线的宽度为8A.B.C.D.

某系统总线的一个总线周期包含4个时钟周期,每个总线周期中可以传送64位数据。若总线的时钟频率为44MHZ,则总线带宽为(43)。A.132MB/sB.88MB/sC.44MB/sD.396MB/s

如存储器的工作频率为333MHz,数据线宽度为32位,每个周期传输1次数据,则存储器的带宽=___【23】____MB/s。若存储器总线采用串行总线,以10位为一个数据帧(包含一个字节的存储数据),则总线带宽=总线频率/___【24】____。

假设某系统总线的一个总线周期包含4个时钟周期,每个总线周期中可以传送64位数据。若总线的时钟频率为133MHz,则总线带宽约为(20)。A.64MBpsB.133MBpsC.256MBpsD.266MBps

设存储器容量为32位,字长64位,模块数m=8,分别用顺序方式和交叉方式进行组织。若存储周期T = 200ns,数据总线宽度为64位,总线传送周期为50ns,则顺序存储器和交叉存储器带宽各是多少?

问答题假定某计算机的CPU主频为80MHz,CPI为4,并且平均每条指令访存1.5次,主存与Cache之间交换的块大小为16B,Cache的命中率为99%,存储器总线宽度为32位。请回答下列问题。 (1)该计算机的MIPS数是多少?平均每秒Cache缺失的次数是多少?在不考虑DMA传送的情况下,主存带宽至少达到多少才能满足CPU的访存要求? (2)假定在Cache缺失的情况下访问主存时,存在0.0005%的缺页率,则CPU平均每秒产生多少次缺页异常?若页面大小为4KB,每次缺页都需要访问磁盘,访问磁盘时DMA传送采用周期挪用方式,磁盘I/O接口的数据缓冲寄存器为32位,则磁盘I/O接口平均每秒发出的DMA请求次数至少是多少? (3)CPU和DMA控制器同时要求使用存储器总线时,哪个优先级更高?为什么? (4)为了提高性能,主存采用4体交叉存储模式,工作时每1/4个存储周期启动一个体。若每个体的存储周期为50ns,则该主存能提供的最大带宽是多少?