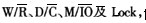

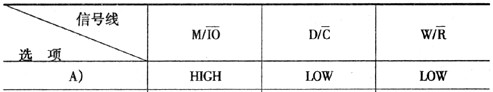

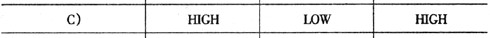

80386有4个总线周期定义信号但主要的总线周期定义了前三个。在I/O写周期,总线周期定义信号状态为( ),在存储器数据读取周期总线信号定义为( ),在存储器指令码读取周期总线信号定义为( )。A.B.C.D.

80386有4个总线周期定义信号

但主要的总线周期定义了前三个。在I/O写周期,总线周期定义信号状态为( ),在存储器数据读取周期总线信号定义为( ),在存储器指令码读取周期总线信号定义为( )。

A.

B.

C.

D.

相关考题:

下面是是关于Pentium 微处理器总线时序的叙述,其中错误的是A.CPU通过总线接口部件完成一次存储器读/写I/0所需要的时间称为总线周期B.Pentium微处器执行流水线式总线周期时,下一个总线周期使用的地址在前一个总线周期传送数据时提供C.Pentium微处器的基本总线周期需要2个或2个以上的总线时钟周期D.Pentium 微处理器的突发式读总线周期由2-1-1-1个时钟周期组成, 共传递5个64位数据

有些文献按下式定义总线数据传输速率 Q=WX+F/N 式中Q为总线数据传输率;W为总线数据宽度(总线位宽用):F为总线工作频率;N为完成一次数据传送所需的总线时钟周期个数。当总线位宽为16位,总线工作频率为8MHz,完成一次数据传送需2个总线时钟周期时,总线数据传输速率Q应为( )。A.16MB/sB.8MB/sC.16MB/sD.8MB/s

80386有4个总线周期定义信号,分别为W/R、D/C、M/IO和LOCK;其中前3个是主要的总线周期定义信号在存储器数据读取周期,各总线周期定义信号为( )。A.W/R=L低电平,D/C=H高电平,M/IO=H高电平B.W/R=L低电平,D/C=H高电平,M/IO=L低电平C.W/R=H高电平,D/C=L低电平,M/IO=H高电平D.W/R=L低电平,D/C=L低电平,M/IO=H高电平

80386有4个总线周期定义信号分别为W/R、D/C、M/IO和LOCK,其中前3个是主要的总线周期定义信号,在FO写周期,各总线周期定义信号为( )。A.W/R=L低电平,D/C=H高电平,M/IO=H高电平B.W/R=L低电平,D/C=H高电平,M/IO=L低电平C.W/R=H高电平,D/C=L低电平,M/IO=H高电平D.W/R=L低电平,D/C=L低电平,M/IO=H高电平

总线规范会详细描述总线各方面的特性,其中( )特性规定了总线的线数,以及总线的插头、插座的形状、尺寸和信号线的排列方式等要素。总线带宽定义为总线的最大数据传输速率,即每秒传输的字节数。假设某系统总线在一个总周期中并行传输4B信息,一个总线周期占用2个时钟周期,总线时钟频率为10MHz,则总线带宽为( )Mbps。A.物理 B.电气 C.功能 D.时间 A.20 B.40 C.60 D.80

80386有4个总线周期定义信号分别为W/R、D/C、M/IO和LOCK,其中前3个是主要的总线周期定义信号,在I/O写周期,各总线周期定义信号为( )。A.W/R=H低电子,D/C=H高电平,M/IO=H高电平B.W/R=L低电平,D/C=H高电平,M/IO=L低电子C.W/R=H高电平,D/C=H低电平,M/IO=L高电平D.W/R=H低电平,D/C=L低电平,M/IO=H高电平

总线规范会详细描述总线各方面的特性,总线带宽定义为总线的最大数据传输速率,即每秒传输的字节数。假设某系统总线在一个总周期中并行传输4B信息,一个总线周期占用2个时钟周期,总线时钟频率为10MHz,则总线带宽为(61)Mbps。A.20B.40C.60D.80

填空题8086正常的存储器读/写总线周期由()个T状态组成,ALE信号在()状态内有效,其作用是()。