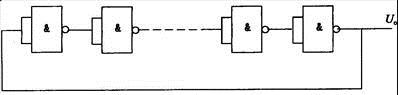

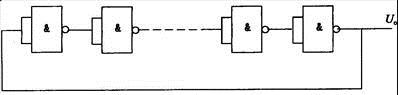

用50个与非门组成的环形多谐振荡器如题图所示,设每个门的平均传输时间tpd=20ns,试求振荡周期T为( )。 A. 20ms B. 2ms C. 4.0ms D. 4ms

用50个与非门组成的环形多谐振荡器如题图所示,设每个门的平均传输时间tpd=20ns,试求振荡周期T为( )。

A. 20ms

B. 2ms

C. 4.0ms

D. 4ms

B. 2ms

C. 4.0ms

D. 4ms

参考解析

解析:环形多谐振荡器是利用闭合回路中的正反馈作用产生自激振荡的,若每级门电路的平均传输延迟时间为tpd,那么n个门的传输时间为ntpd,则输出信号的振荡周期为:T=2ntpd。代入数据得:T=2×50×20×10-9=2ms。

相关考题:

CMOS集成施密特触发器组成的电路如图(a)所示,该施密特触发器的电压传输特性曲线如图(b)所示,该电路的功能为( )。 A. 双稳态触发器 B. 单稳态触发器 C. 多谐振荡器 D. 三角波发生器

设某机平均执行一条指令需要两次访问内存,平均需要三个机器周期,每个机器周期包含4个节拍周期。若机器主频为25MHz,试回答:若每次访问内存需要插入2个等待节拍周期,则平均执行一条指令的时间是又多少?

问答题设某机平均执行一条指令需要两次访问内存,平均需要三个机器周期,每个机器周期包含4个节拍周期。若机器主频为25MHz,试回答:若访问主存不需要插入等待周期,则平均执行一条指令的时间为多少?

问答题设某机平均执行一条指令需要两次访问内存,平均需要三个机器周期,每个机器周期包含4个节拍周期。若机器主频为25MHz,试回答:若每次访问内存需要插入2个等待节拍周期,则平均执行一条指令的时间是又多少?

单选题利用门电路的传输时间,可以把()个与非门首尾相接,组成多谐振荡器。A8B7C6D4