试分别画出图4-30(a)电路输出端Y、Z和图4-30(b)电路输出端Q2的波形.输入信号A和CP的电压波形如图4-30(c)所示,各触发器的初始状态为0.

试画出图4-6所示电路图在给定输入时钟作用下的输出波形.设触发器的初态为0.

题7-12图所示无源一端L的电压、电流如下列各式所示,试求每种情况下的等效阻抗和等效导纳:画出等效电路图并求出等效电路参数。

分析图题7.10所示电路,画出它们的状态图和时序图,指出各是几进制计数器。

试画出图题2-1 (a) 所示电路在输入图题2-1 (b)波形时的输出端B、C的波形。图题2-1

试画出图题2-3 (a) 所示电路在输入图题2-3 (b)波形时的输出端X、Y的波形。图题2-3

试分析图题3-5所示MOS电路的逻辑功能,写出Y端的逻辑函数式,并画出逻辑图。

逻辑电路与其输入端的波形如图题4-5所示,试画出逻辑电路输出端Y的波形。图题4-5

对于图题4-21所示波形作为输入的电路,试画出其输出端的波形。

画出图题5-9所示的正边沿触发JK触发器输出Q端的波形,输入端J、K与CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-14所示各触发器输出Q端的波形,CLK、 A和B的波形如图所示。(设Q初始状态为0)

试画出图题5-15所示各触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

画出图题5-4所示的电平触发D触发器输出Q端的波形,输入端D与CLK的波形如图所示。(设0初始状太为0)

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

画出图题5-10所示的JK触发器输出端Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

画出图题5-6所示的边沿D触发器输出Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

试画出图题5-12所示电路输出端Q1、Qo端的波形,CLK 的波形如图所示。(设Q初始状态为0)

画出图题5-8所示的JK触发器输出Q端的波形,输入端JK与CLK的波形如图示。(设Q初始状态为0)

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

图题6-15所示的是5位右移寄存器与输入信号DATA、时钟CLK的波形图,若寄存器初始状态为00000,试画出寄存器输出Q4~Q0的波形图。

图题6-16所示的是8位右移寄存器74HC164符号、输入信号DATA、时钟CLK的波形图,若寄存器初始状态为0000000试画出寄存器输出QFQA的波形图。

图题6-17所示的是8位右移寄存器74HC164与共阳数码管的连接图,其输入信号DATA、时钟CLK的波形图,若寄存器初始状态为0000000,试画出74HC164输出QF~QA的波形图,并说明数码管显示的数字是多少?

图题6-18所示的是并入串出8位右移寄存器74HC165的连接图,以及输入信号CLKINH、移位/置数信号SH/与时钟CLK的波形图,若74HC165并入数据为11100101,试画出74HC165输出Y的波形图。

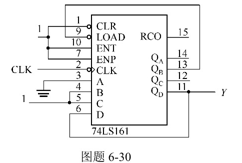

试写出图题6-4所示电路的驱动方程、状态方程、输出方程与状态图,并按照所给波形画出输出端Y的波形。