试画出图4-6所示电路图在给定输入时钟作用下的输出波形.设触发器的初态为0.

试画出图题2-1 (a) 所示电路在输入图题2-1 (b)波形时的输出端B、C的波形。图题2-1

试画出74HC与74LS系列逻辑门电路的输出逻辑电平与输入逻辑电平示意图。

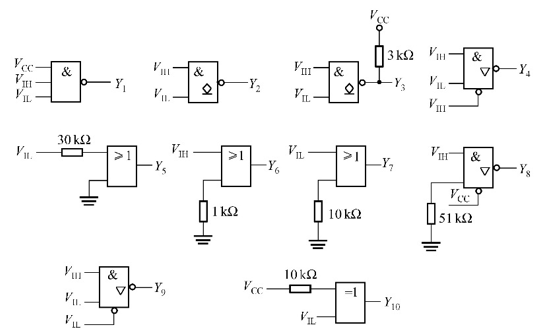

试确定图题 3-25所示74HC门电路的输出状态(设电源Vcc为5 V)。图题3-25

试确定图题3-26所示74LS门电路的输出负载是灌电流还是拉电流,并确定最大电流值。图题3-26

写出图题3-27所示电路的逻辑函数式。若是每个门的loL (max)= 20mA, VoL(max)=0.25V,假设Y端连接10个TTL负载。试求电源电压是5V情况下的最小上拉电阻值。图题3-27

画出图题5-9所示的正边沿触发JK触发器输出Q端的波形,输入端J、K与CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-14所示各触发器输出Q端的波形,CLK、 A和B的波形如图所示。(设Q初始状态为0)

试画出图题5-15所示各触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

试画出图题5-20所示电路中触发器输出Q1、Q2端的波形,CLK的波形如图所示。(设Q初始状态为0)

画出图题5-11所示的脉冲JK触发器输出Q端的波形,输入端J K与CLK的波形如图所示。(设Q初始状态为0)

画出图题5-10所示的JK触发器输出端Q端的波形,CLK的波形如图所示。(设Q初始状态为0)

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

画出图题5-1所示的SR锁存器输出端Q、端的波形,输入端与的波形如图所示。(设Q初始状态为0)

试画出图题5-16所示触发器输出Q端的波形,CLK 的波形如图所示。(设Q初始状态为0)

试画出图题5-12所示电路输出端Q1、Qo端的波形,CLK 的波形如图所示。(设Q初始状态为0)

画出图题5-8所示的JK触发器输出Q端的波形,输入端JK与CLK的波形如图示。(设Q初始状态为0)

画出图题5-5所示的边沿触发D触发器输出端Q端的波形,输入端D与CLK的波形如图所示。(设Q初始状态为0)

图题6-15所示的是5位右移寄存器与输入信号DATA、时钟CLK的波形图,若寄存器初始状态为00000,试画出寄存器输出Q4~Q0的波形图。

图题6-16所示的是8位右移寄存器74HC164符号、输入信号DATA、时钟CLK的波形图,若寄存器初始状态为0000000试画出寄存器输出QFQA的波形图。

试写出图题6-4所示电路的驱动方程、状态方程、输出方程与状态图,并按照所给波形画出输出端Y的波形。

试计算图题11-4所示电路的输出电压Vo。答案:由图可知,D3~Do=0101因此输出电压为:5.8位输出电压型R/2R电阻网络D/A转换器的参考电压为5V,若数字输入为10011001,该转换器输出电压Vo是多少?

图所示电路为TTL门电路,输出状态为( )。A.低电平B.高电平C.高阻态D.截止状态

如果将TTL逻辑门电路的输出采用下列接法会产生什么样的结果,试说明原因? (1)输出直接接地; (2)输出端直接接电源VCC=+5V; (3)多个输出端并接一起。