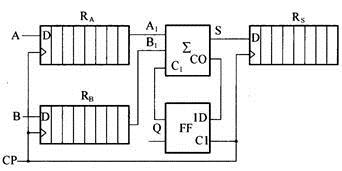

时序电路如题图所示,其中RA、RB\R3均为8位移位寄存器,其余电路分别为全加器和D触发器,那么,该电路又具有( )功能。 A. 实现两组8位二进制串行乘法功能 B. 实现两组8位二进制串行除法功能 C. 实现两组8位二进制串行加法功能 D. 实现两组8位二进制串行减法功能

时序电路如题图所示,其中RA、RB\R3均为8位移位寄存器,其余电路分别为全加器和D触发器,那么,该电路又具有( )功能。

A. 实现两组8位二进制串行乘法功能

B. 实现两组8位二进制串行除法功能

C. 实现两组8位二进制串行加法功能

D. 实现两组8位二进制串行减法功能

B. 实现两组8位二进制串行除法功能

C. 实现两组8位二进制串行加法功能

D. 实现两组8位二进制串行减法功能

参考解析

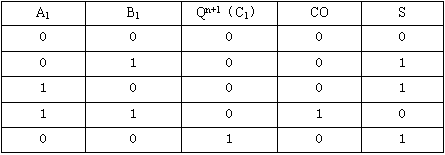

解析:C1=Q,Q=D,Qn+1=D=CO,CO为进位标志,真值表如题解表所示。

从逻辑关系上分析可知该电路实现了两组8位二进制串行加法功能。

从逻辑关系上分析可知该电路实现了两组8位二进制串行加法功能。

相关考题:

CMOS集成施密特触发器组成的电路如图(a)所示,该施密特触发器的电压传输特性曲线如图(b)所示,该电路的功能为( )。 A. 双稳态触发器 B. 单稳态触发器 C. 多谐振荡器 D. 三角波发生器

单选题下列哪组不属于时序逻辑电路()A主从触发器,T触发器B数码寄存器,移位寄存器C异步计数器,同步计数器D半加器,全加器