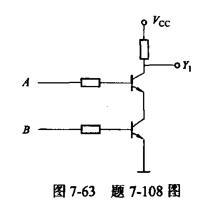

如图7-63所示,输出端F1的逻辑表达式为()。

如图7-63所示,输出端F1的逻辑表达式为()。

参考解析

解析:正确答案是B。

提示:掌握与非门的组成结构,只有A和B都为高电平时,Y1为0。

提示:掌握与非门的组成结构,只有A和B都为高电平时,Y1为0。

相关考题:

●某逻辑电路有两个输入端分别为X和Y,其输出端为Z。当且仅当两个输入端X和Y同时为0时,输出Z才为0,则该电路输出Z的逻辑表达式为 (9) 。(9) A.X-YB. X+YC.X○+YD.X·Y

组合逻辑电路分析过程一般按下列步骤进行:①根据给定的逻辑电路,从输入端开始,逐级推导出输出端的逻辑函数表达式。②根据输出函数表达式列出真值表。③用文字概括出电路的逻辑功能。() 此题为判断题(对,错)。

如图7-59所示,输出F与输入A、B逻辑关系是()。