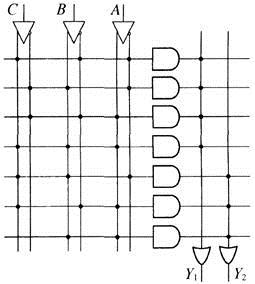

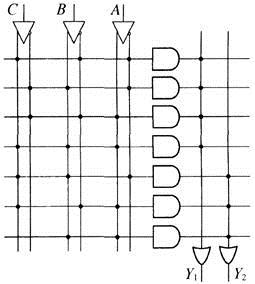

PLA编程后的阵列图如图所示,该函数实现的逻辑功能为( )。 A. 多数表决器 B. 乘法器 C. 减法器 D. 加法器

PLA编程后的阵列图如图所示,该函数实现的逻辑功能为( )。

A. 多数表决器

B. 乘法器

C. 减法器

D. 加法器

B. 乘法器

C. 减法器

D. 加法器

参考解析

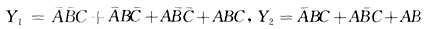

解析:PLA阵列图中,有圆点表示连接,没有圆点表示不连接,图的左半部分为AND逻辑阵列,右半部分为OR逻辑阵列,由此可写出阵列的逻辑表达式为:

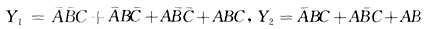

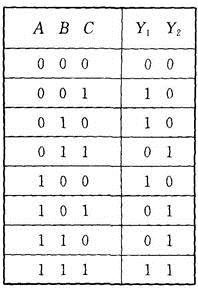

真值表如题解图所示。其中Y1为和位,Y2为进位。由图可知当ABC为100、010、001、111时,Y1Y2输出为01,当ABC为110、011、101时,Y1Y2输出为10,根据输入输出关系,可得逻辑函数表达式为Y1Y2=A+B+C,其实现的逻辑功能为全加器。

真值表如题解图所示。其中Y1为和位,Y2为进位。由图可知当ABC为100、010、001、111时,Y1Y2输出为01,当ABC为110、011、101时,Y1Y2输出为10,根据输入输出关系,可得逻辑函数表达式为Y1Y2=A+B+C,其实现的逻辑功能为全加器。

相关考题:

关于可编程逻辑阵列PLA,下列说法正确的是()。A、PLA结构是与门阵列固定连接,而或门阵列可编程B、PLA结构是或门阵列固定连接,而与门阵列可编程C、PLA结构是与门阵列和或门阵列都可以编程D、PLA中,一个地址码对应的存储单元是唯一的

单选题关于可编程逻辑阵列PLA,下列说法正确的是()。APLA结构是与门阵列固定连接,而或门阵列可编程BPLA结构是或门阵列固定连接,而与门阵列可编程CPLA结构是与门阵列和或门阵列都可以编程DPLA中,一个地址码对应的存储单元是唯一的

填空题PLA的与阵列可编程,或()。