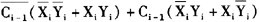

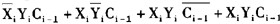

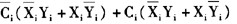

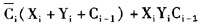

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生本位和S,以及向高位的进位Ci的逻辑电路。(51)和(52)分别是Si和Ci的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(53)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i=1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,C0=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(54)和(55)。A.B.C.D.

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生本位和S,以及向高位的进位Ci的逻辑电路。(51)和(52)分别是Si和Ci的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(53)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i=1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,C0=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(54)和(55)。

A.

B.

C.

D.

相关考题:

全加器是由两个加数Xi和Yi以及低位来的进位Ci-1作为输入,产生向高位的进位Ci以及本位利Si的逻辑电路。(65)和(66)分别是进位和本位和的正确逻辑表达式。全加器亦可通过半加器来实现,此时Si=(67)。若某计算机采用8位带符号补码表示整数,则可由8个全加器(i =1,2,……8,i=8为最高位,即符号位)串接构成8位加法器,CO=0。该加法器有一个状态寄存器,记录运算结果的状态。其中,N和V分别表示符号位与溢出标志位,则其逻辑表达式分别为(68)和(69)。A.XiYi+XiCi-1+YiCi-1B.XiYi+XiSj+YiSiC.XiYi+XiCi-1+YiCi-1D.(XiYi+XiYi).Ci-1

单选题74181算术逻辑单元含有()位并行进位全加器。A3B4C5D6