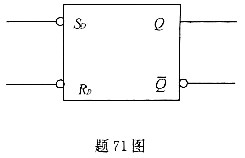

在图示逻辑电路中,触发器的初始状态是“1”态,当RD端保持高电平,在SD端加一负脉冲时,触发器的新态是( )。A.翻转到“0”态B.保持“1”态C.先翻转到“0”,马上回到“1”态D.无规律翻转不能确定

在图示逻辑电路中,触发器的初始状态是“1”态,当RD端保持高电平,在SD端加一负脉冲时,触发器的新态是( )。

A.翻转到“0”态

B.保持“1”态

C.先翻转到“0”,马上回到“1”态

D.无规律翻转不能确定

B.保持“1”态

C.先翻转到“0”,马上回到“1”态

D.无规律翻转不能确定

参考解析

解析:基本RS触发器

相关考题:

若R和S为两个输入端,下面是同步触发器说法正确的是()。A、在CP=1期间,如R=0、S=1,触发器为“1”态B、在CP=1期间,如R=1、S=0,触发器为“0”态C、在CP=1期间,如R=0、S=0,触发器保持原状态D、在CP=1期间,如R=1、S=0,触发器为“1”态E、在CP=1期间,如R=0、S=1,触发器为“0”态

若R和S为两个输入端,下面是“与非”型基本RS触发器说法正确的是()。A、当R=S=1时,触发器保持原状态不变B、当S=0、R=1使触发器置1C、当S=1、R=0使触发器置0D、当R=S=0时,将不能确定触发器是处于1态还是0态E、当S=1、R=0使触发器置1

TTL型触发器的直接置0端Rd、置1端Sd正确用法是()A、都接高电平“1”B、都接低电平“0”C、逻辑符号有小圆圈时,不用时接高电平“1”,没有小圆圈时,不用时接低电平“0”D、没有记忆功能

单选题当集成维持—阻塞D型触发器的异步置0端RD=0时,则触发器的次态()。A与CP和D有关B与CP和D无关C只与CP有关D只与D有关