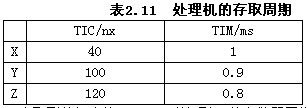

设有三个指令系统相同的处理机X、Y和乙它们都有4KB的高速缓冲存储器和 32 MB的内存,但是其存取周期都不一样,如表2.11所示(TIC和TIM分别表示I处理机 Cahce存取周期和主存存取周期)。若某段程序所需指令或数据在Cache中取到的概率为P=0.5,则处理机X的存储器平均存取周期为(50)ms。假定指令执行时间与存储器的平均存取周期成正比,此时三个处理机执行该段程序由快到慢的顺序为(51)。若P=0.65,则顺序为(52)。若P=0.8,则顺序为(53)。若P=0.85,则顺序为(54)。A.0.2B.0.48C.0.52D.0.6

设有三个指令系统相同的处理机X、Y和乙它们都有4KB的高速缓冲存储器和 32 MB的内存,但是其存取周期都不一样,如表2.11所示(TIC和TIM分别表示I处理机 Cahce存取周期和主存存取周期)。

若某段程序所需指令或数据在Cache中取到的概率为P=0.5,则处理机X的存储器平均存取周期为(50)ms。假定指令执行时间与存储器的平均存取周期成正比,此时三个处理机执行该段程序由快到慢的顺序为(51)。

若P=0.65,则顺序为(52)。

若P=0.8,则顺序为(53)。

若P=0.85,则顺序为(54)。

A.0.2

B.0.48

C.0.52

D.0.6

相关考题:

在CPU执行一段程序的过程中,Cache的存取次数为4600次,由主存完成的存取次数为400次。若Cache的存取周期为5ns,主存的存取周期为25ns,则CPU的平均访问时间为______ns。A.5.4B.6.6C.8.8D.9.2

设有三个处理机A,B和C。它们各有一个高速缓冲存储器CA,CB和CC,并各有一个主存储器MA,MB和MC,其性能如表2-5所示。假定三个处理机的指令系统相同,它们的指令执行时间与存储器平均存取周期成正比。如果执行某个程序时,所需的指令或数据在缓冲存储器中取到的概率是P=0.6,那么这三个处理机按处理速度由快到慢的顺序应当是 (59) 。当P=0.75时,则其顺序应当是(60)。当P=0.95时,则其顺序应当是(61)。当P=(62)时,处理机A和B的处理速度最接近。当P=(63)时,处理机B和C的处理速度最接近。A.A,B,CB.A,C,BC.B,A,CD.B,C,AE.C,B,A

在CPU执行一段程序的过程中,Cache的存取次数为4600次,由主存完成的存取次数为400次。若 Cache的存取周期为5ns,CPU的平均访问时间为6.6ns,则主存的存取周期为(3)ns。A.18.6B.21.7C.23.8D.25

在CPU执行一段程序的过程中,cache的存取次数为3800次,由主存完成的存取次数为200次。若cache的存取周期为5ns,主存的存取周期为25ns,则cache的命中率为(1);CPU的平均访问时间为(2)ns。A.0.93B.0.95C.0.97D.0.99

CPU配合Cache高速缓冲存储器工作,如果内存的存取周期时间为60ms,高速缓存的存取周期时间为15ms,命中率为90%.,则高速缓冲单元的平均存取时间均为( )。A.22.75msB.21.75msC.18.5msD.19.5ms

在主存和CPU之间增加Cache的目的是(17)。在CPU执行一段程序的过程中,Cache的存取次数为2250次,由内存完成的存取次数为250次。若Cache的存取周期为6ns,内存的存取周期为24ns,则Cache的命中率为(18),CPU的平均访问时间为(19)ns。A.提高内存工作的可靠性B.扩展内存容量C.方便用户操作D.提高CPU数据传输速率

假设CPU执行某段程序时,共访问Cache命中1000次,访问主存20次。已知Cache的存取周期是20ns,主存的存取周期为100ns。则Cache-主存系统的命中率和平均访问时间分别为A.0.9804,21.568nsB.0.9800,21.568nsC.0.9800,21.600nsD.0.9800,21.600ns

主存储器的存储周期和存取时间相同。